知识|PXI总线仪用模块的设计与实现

介绍了PXI总线仪用模块的结构和特点,描述了低成本FPGA器件开发模块的各种功能。重点描述了PXI仪用模块必须具有的PCI/PXI总线接口、精密时基和触发控制器的实现,最后探讨了PXI仪用模块针对EMC应采取的措施。实际应用表明所设计的PXI仪用模块完全符合PXI硬件规范,达到了设计要求。

PXI规范定义了一种功能强大的仪器平台,用于测量和自动化领域。PXI是基于CPCI平台、并附加仪器规范(如EMI/RFI、机械接口、冷却、触发、设备同步、软件接口等)所构成的仪用平台。测试系统的同步和控制是众多功能测试应用的先决条件,它们依赖于事件检测、激励/响应或相位相关,而PXI提供了满足这种要求所需的电气扩展信号,包括用于仪器同步的系统参考钟PXI_CLK10、PXI TRIG总线、时间非常精密的PXI_STAR触发总线以及用于相邻单板通信的局部总线。PXI仪用系统较GPIB、VXI等仪器系统具有较好的性价比,因而越来越多地被从事自动测试测量的工程技术人员选用或开发PXI仪器。如何设计符合PXI规范特别是仪用要求的PXI模块就成了关键。本文在PXI规范及PXI硬件规范的基础上,借助多通道高速数据采集模块的设计及其应用,揭示PXI仪用模块的设计需要的关键技术。

1. PXI总线数据采集模块的结构

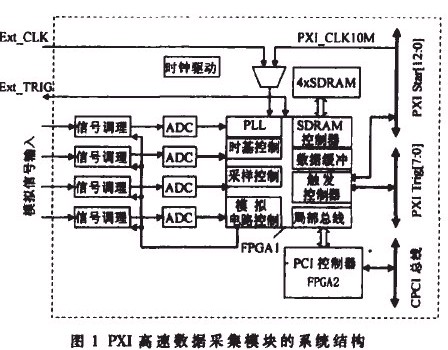

PXI总线四通道高速数据采集模块是高速、高精度的自动测试模块。整个采集模块从电路上可分为模拟信号调理及A/D转换、系统控制器、PCI总线接口等几个部分。系统控制器包括模拟信号的控制与设置、时基源控制、触发源设置、触发模式设置、采样控制、数据缓冲、数据存储、数据传输等。

PXI高速数据采集模块结构如图1所示。信号调理(Conditioning)及A/D转换部分决定了模拟信号采集的性能,时基控制电路为模块和其他PXI模块提供采样和同步基准钟,触发控制器用于接收或发送触发信号,数据缓冲和SDRAM控制器用于数据在板缓存,局部总线控制器用于主机与各控制器进行通信。各控制器均采用Verilog HDL实现。其中,ADC选用AD9235-65,FPGA1、FPGA2分别选用ALTERA公司的EP1C6Q248和EP1C6Q144,在板数据缓存选用Microchip公司的MT48LC8M16A2。

采集模块有四个模拟通道,每个模拟通道都有独立的信号调理电路、ADC和在板数据缓存。在系统控制器FPGA1的控制下,当满足预设的触发条件时,将A/D转换后的数据送入SDRAM,然后计算机将数据读入进行分析和保存。

2 .PCI/PXI接口的实现

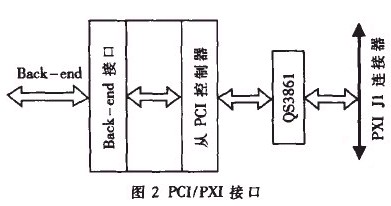

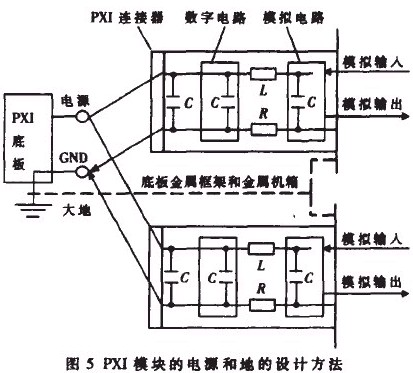

PCI/PXI接口需要设计PCI控制器、Back-end接口,并且需要满足CPCI规范的电气要求。这些电气要求包括电源解耦、信号分支(stub)终结、信号分支长度约束、热插拔、3.3V/5V信号环境等。多通道高速数据采集模块采用Verilog HDL在EP1C6Q144中实现32位Slave PCI控制器、Back-end接口,通过它来实现仪器模块与计算机之间的通信。如图2所示

通常为满足电信等应用,当CPCI单板出现故障时,要求在整个系统不停机的情况下允许带电拔出故障板并插入备份板进行维护。一般情况下PXI仪器不需要热插拔,3U尺寸的PXI卡外形又很小,布局布线不便。本设计没有采用热插拔。PXI模块的PCI信号应能兼容PCI3.3V/5V信号环境。如果PXI底板的码键是镉黄色则是3.3V信号环境,亮蓝色则是5V信号环境,没有码键则为3.3V/5V通用信号环境。本设计采用IDT的电平转换芯片QS3861,以兼容PCI3.3V和PCI5V信号环境。同时,芯片导通时的典型阻抗为10Ω,满足信号stub终结电阻的要求。

3 .PXI仪器同步机制的实现

被测对象(DUT)可能有数个缓变信号、混合信号,或众多个相互关联的信号。数个缓变信号的测试只需简单测试设备就可以完成,实时时钟也可以保证时间精度。混合信号和众多相互关联信号的测试,既有测试也有激励,需要一台或多台仪器,所构成的测试系统就是综合测试系统,系统中的每个模块必须具有精确的同步和控制以达到同时操作。从这个角度考虑,通常要求仪器底板提供一个精密的系统参考钟、一套触发总线、通过前面板提供接收或发送到其他仪器的时钟和触发信号接口。PXI底板包括系统参考钟、PXI触发总线、星形触发总线等资源。开发人员可以利用这些资源设计精密而灵活的时基和触发控制器,以实现多台仪器的同步和控制。

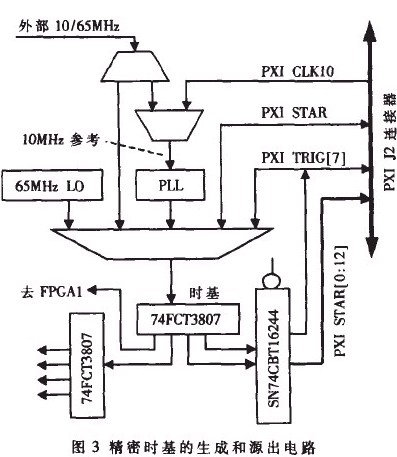

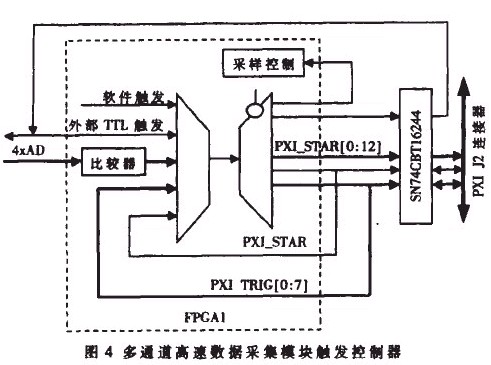

(1)PXI底板提供了一个公共的参考时钟,每个外设槽都有一个PXI_CLK10 TTL钟,从钟源到每个槽的布线等长,两槽之间的信号偏移小于1ns。 (2)PXI 规范定义了八个触发信号用于模块间的同步和通信,时钟、触发和握手信号共享这个触发总线,覆盖一个总线段。PXI TRIG总线允许传输不同频率的采样时钟,多个模块可以直接共享这个采样时钟,其时钟脉冲的倾斜精度小于10ns。PXI规范建议采用PXI_TRIG[7]信号线,用于发送或接收采样时钟。在上电时,这些信号应处于高阻态。 (3)PXI提供了一个超高性能的星形触发总线,同参考时钟一样,星形触发信号是由位于第一外设槽的星形触发控制器将信号点对点沿着等长的信号线传送给其他外设槽,其信号抖动小于1ns,覆盖两个总线段。 对于PXI仪用模块的设计,应考虑其在综合测试系统中的应用,前面板至少需要一个时钟输入、一个双向触发线,结合仪器本地自洽的时钟和触发总线,方能建立一套完备的同步机制。 3.1 PXI仪用模块精密时基的设计 通常一个PXI仪用模块应有三个时基源: PXI_CLK10参考时钟、外部(前面板)10MHz参考时钟或65MHz时基、PXI_TRIG[7]或PXI_STAR提供的采样钟。模块精密时基的设计包括时基的生成和传送。由于A/D转换器的采样时钟频率为65MHz,所以模块的时基频率可以定为65MHz。如果利用10MHz参考时钟,还必须通过PLL进行倍频,显然倍频系数不是整数。当不同的模块利用PXI_CLK10获取65MHz采样钟作为时基时,不同模块间的采样钟很难达到相位同步。为了保证所有模块同步,如前所述,可将这个采样钟通过PXI_TRIG[7]、PXI_STAR[0:12]传送给其他外设槽。对于多台仪器的同步应用,最好通过用户前面板由外部提供时基源。 由于有多个时基源,且通常时钟的电平是TTL电平,可采用5V耐压的电平转换多路复用/解复器进行选择。这里选用SN74CB3T3253和SN74CBT16244,其传播时延均小于0.25ns。EP1C6Q248内部有两个PLL,一个PLL用来从10MHz参考钟获取时基,一个用于获取数据传输和SDRAM控制器的80MHz时钟。精密时基的获取和源出电路如图3所示。时基源的选择和时基信号的源出由用户通过软件进行配置。

评论排行