EDA⁺缺陷预测赋能先进封装可靠性前置,硅芯科技亮相先进封装可靠性技术大会

【ZiDongHua 之“设计自动化”标注关键词:硅芯科技 高质量发展 EDA 集成电路 】

EDA⁺缺陷预测赋能先进封装可靠性前置,硅芯科技亮相先进封装可靠性技术大会

11月26日至27日,由广东省集成电路行业协会、未来半导体主办的先进封装可靠性技术暨互连材料大会在广州隆重举行。硅芯科技创始人兼首席科学家赵毅博士出席盛会,并在“先进封装可靠性技术大会”上发表了题为“EDA+驱动的2.5D/3D先进封装可靠性设计仿真建模验证新路径”的主题报告,介绍基于EDA+新范式下的先进封装可靠性发展新路径,驱动产业高质量发展。

大会现场

本次大会以“多维互连 可靠赋能”为主题,紧密围绕“半导体互连材料”与“先进封装可靠性技术”两大核心,汇聚了来自全国半导体领域的专家学者、企业代表及行业精英近500人,不仅搭建了技术交流与成果展示的平台,更为打造“中国集成电路第三极”重要支点注入新动能。工业和信息化部电子第五研究所副所长胡湘洪、广东省集成电路行业协会会长陈卫出席大会并致辞。

大会开幕式

后摩尔时代,先进封装技术凭借超高互连密度和优异的工艺兼容性,成为支撑AI算力等关键应用的基石,但其复杂的多层互连、多材料耦合结构也带来了严峻的可靠性挑战。工艺与设计失配、电-热-力协同壁垒、异质Chiplet互连界面问题等,已成为制约产业高质量发展的主要瓶颈。

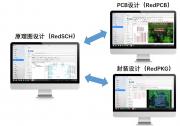

对此,赵毅博士指出,传统设计验证方法已难以应对,必须重构先进封装范式,将可靠性从设计流程的后端检验环节,前置到系统架构环节中。这与硅芯科技近期提出的“2.5D/3D EDA+新范式”理念契合,即通过构建跨工艺、跨芯粒、跨物理场的系统协同设计体系,实现系统级的、可预测的可靠性保障。

跨工艺协同奠定可靠性制造基石新范式强调“以工艺为基础”,在架构规划阶段即依据工艺约束进行Chiplet划分与布局,从源头规避制造失配,实现“可制造性即可靠性”的前置化。跨芯粒协同保障系统级互连可靠性通过专用工具链,对互连规划与电-热-力耦合进行协同仿真与优化,直接应对高速接口信号完整性、堆叠热应力等系统级互连失效风险。跨物理场协同实现可靠性前瞻预测与闭环优化在设计早期即进行多物理场耦合仿真与循环分析,任何潜在风险均可实时反馈至设计端进行闭环优化,使可靠性成为可前瞻预测、可持续优化的主动设计目标。

赵毅博士演讲瞬间

“2.5D/3D EDA+新范式”将可靠性系统地内嵌于设计生命周期,实现了从设计、仿真、建模到验证的全链条闭环,为提升国产高性能芯片的成熟度与竞争力,驱动先进封装产业高质量发展,提供了至关重要的核心支撑。

大会现场

END

关于硅芯

珠海硅芯科技有限公司主要从事新一代2.5D/3D堆叠芯片EDA软件设计的研发及产业化。三维集成电路(堆叠芯片)设计EDA是具有重要意义的技术创新产品,通过堆叠芯片设计实现更高性能、更高集成度、更高可靠性和更低功耗的芯片系统,不仅能够填补国产芯片EDA软件的差距,同时借助2.5D/3D堆叠芯片的行业趋势,助力国产芯片设计行业产业升级,推动RISC-V, AI, GPU, CPU, NPU等各类芯片及终端应用领域发展。

我要收藏

点个赞吧

转发分享

评论排行